北大电子学院张志勇课题组提出集成电路用碳纳米管材料要求

硅基商用晶体管尺寸的缩减伴随着物理极限、功耗、成本等多重挑战。新原理、新结构、新材料器件亟需引入,以满足集成电路对集成度和算力的需求。半导体型阵列碳纳米管(A-CNT)具有高载流子迁移率、超薄体、对称的能带结构,基于此材料制备出的互补金属氧化物半导体场效应晶体管(CMOS FET)展示出几乎对称的电学性能(nSciencen 368, 850, 2020; nNature Electronicsn 4, 405, 2021; nACS Nanon 16, 21482, 2022),90nm节点A-CNT FET的性能超越了硅基28nm节点器件,并展现出进一步缩减至10nm节点的潜力(nNature Electronicsn 6, 506-515, 2023),是构建未来集成电路的理想器件。实现碳基集成电路技术从原型器件到工程化集成的跨越,需要晶圆级高质量的半导体碳纳米管材料。经过30余年的发展,学术界已经发展了体系丰富的碳纳米管材料制备技术,然而,目前电子级碳纳米管材料,特别是A-CNT材料一直缺乏具体要求和标准,在一定程度上阻碍了碳基集成电路的发展。

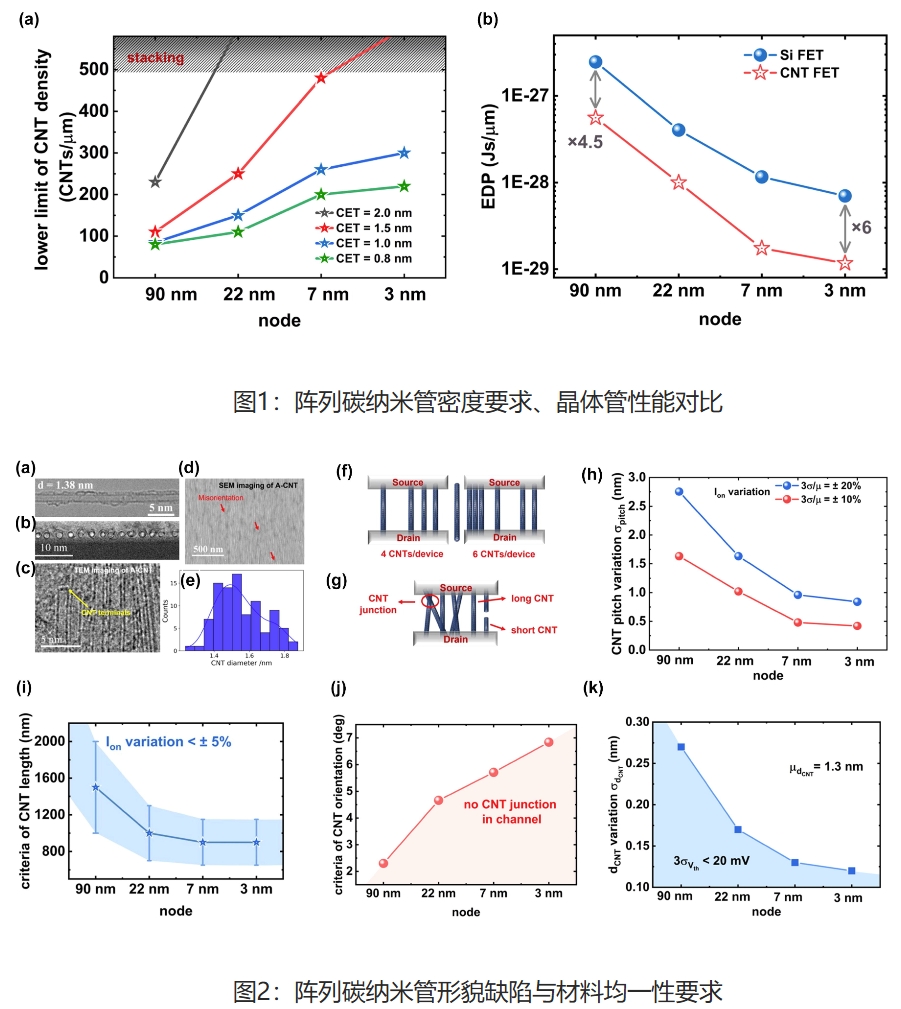

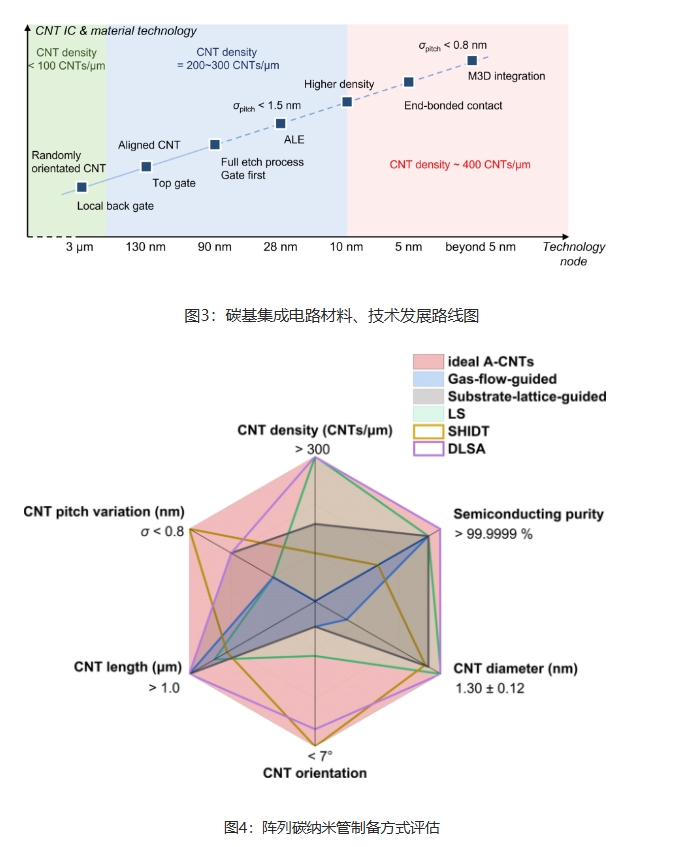

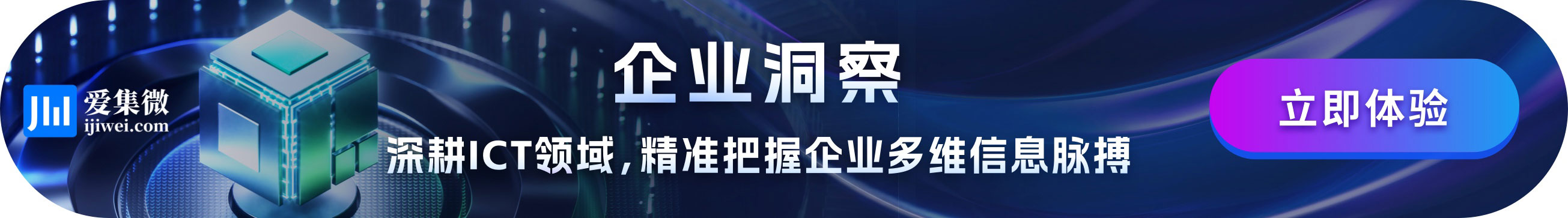

近日,北京大学电子学院、碳基电子学研究中心张志勇教授课题组和浙江大学材料科学与工程学院金传洪教授课题组合作,从高性能电子器件和集成电路角度,对A-CNT材料进行深入研究与系统分析,提出了精细的要求和标准。通过实验结果结合理论计算,团队对90nm、22nm、7nm、3nm技术节点的A-CNT FET的电学性能进行预测,并基于未来集成电路对晶体管性能的要求,提出对阵列碳纳米管密度的要求(图1a)。研究结果表明,相同节点下,A-CNT CMOS器件相比于硅基CMOS器件展现出4-6倍的能量延时积(EDP)优势(图1b),凸显了其在未来高性能数字集成电路中的应用潜力。团队进一步对目前A-CNT中存在的形貌缺陷进行表征(图2a—e),讨论各形貌缺陷对晶体管电学性能波动的影响,并结合集成电路对器件均一性的要求,对碳管形貌提出要求(图2f—k)。在此基础上,他们提出了电子级A-CNT材料的标准,包括碳管密度、直径、长度、半导管纯度、取向、相邻管间距变化等关键参数,并展望了未来碳基集成电路技术和材料的协同优化路线(图3),对目前学术界发展的几种典型A-CNT制备方式进行了综合评估(图4),为电子级A-CNT材料的制备技术发展提供了重要指导。