北科大及张跃院士团队在二维半导体材料低功耗器件架构方面取得进展

集微网消息,近日,北京科技大学张铮教授团队和张跃院士团队在二维半导体材料低功耗器件架构方面取得进展。研究成果以“自偏置二硫化钼晶体管基同质结负载型反相器用于亚皮瓦级计算”为题,于2024年1月8日发表在《自然·电子》上。

随着集成电路制程节点的不断推进,传统硅基CMOS器件面临尺寸微缩下高泄漏电流导致的芯片静态功耗无法抑制的重大挑战。二维过渡金属硫族化合物(TMDCs)材料具有突破尺寸微缩极限的稳定结构、优异的输运性能和对短沟道效应的免疫性,是后摩尔时代最具竞争力的集成电路非硅沟道材料之一。

然而,二维半导体材料无法通过化学掺杂工艺构筑稳定的CMOS器件,因此,亟待开发基于二维材料本征优势的新集成器件架构,研制满足低功耗应用需求的新型逻辑电子器件。

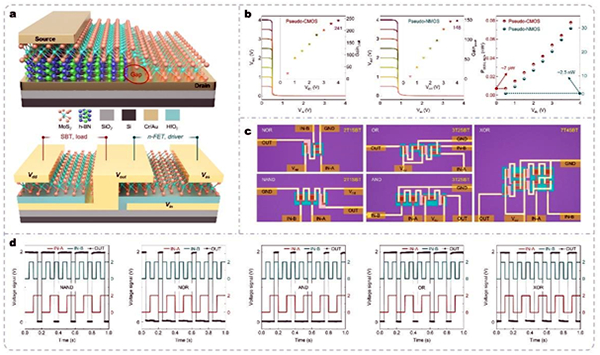

根据国家自然科学基金委员会工程与材料科学部的报道,针对上述挑战,张铮教授团队和张跃院士团队聚焦二维过渡金属硫族化合物材料在集成电路的应用需求,瞄准这类材料无法实现稳定的低功耗CMOS器件架构的关键问题和挑战,并率先发现了范德华气隙势垒对单层二硫化钼(MoS2)电子输运行为的非对称调控特性,设计构筑了自偏置同质结二极管。基于该发现,团队创新提出了通过共电极设计将单层二硫化钼构筑的自偏置同质结二极管与N型场效应晶体管互连组成结型CMOS(pseudo-CMOS)逻辑反相器的新器件架构(图)。

通过气隙势垒有效抑制了漏电流,使得器件的静态功耗显著降低到亚皮瓦级,仅约为传统CMOS逻辑反相器的1%、NMOS逻辑反相器的0.3%。为了验证二维范德华结型CMOS技术在大规模电路制造应用的可行性,团队设计研制了结型CMOS通道晶体管逻辑电路,实现了全摆幅逻辑功能,且执行相同逻辑功能,节省了超过80%的晶体管数量。同时进一步研究设计出了自偏置范德华气隙势垒的结型CMOS集成器件架构,验证了单极性二维半导体材料在超低功耗逻辑计算的可行性,为二维半导体材料在未来集成电路发展提供了新的思路。

该研究得到了国家自然科学基金项目的资助。(校对/武守哲)