台积电半导体晶粒WoW 3D封装及其形成方法专利公开

集微网消息,据天眼查消息,台积电一项“半导体晶粒封装及其形成方法”专利于1月16日公开,公布号:CN117410278A。该专利属3D封装领域WoW(晶片叠晶片)方式,可减少漏电现象。

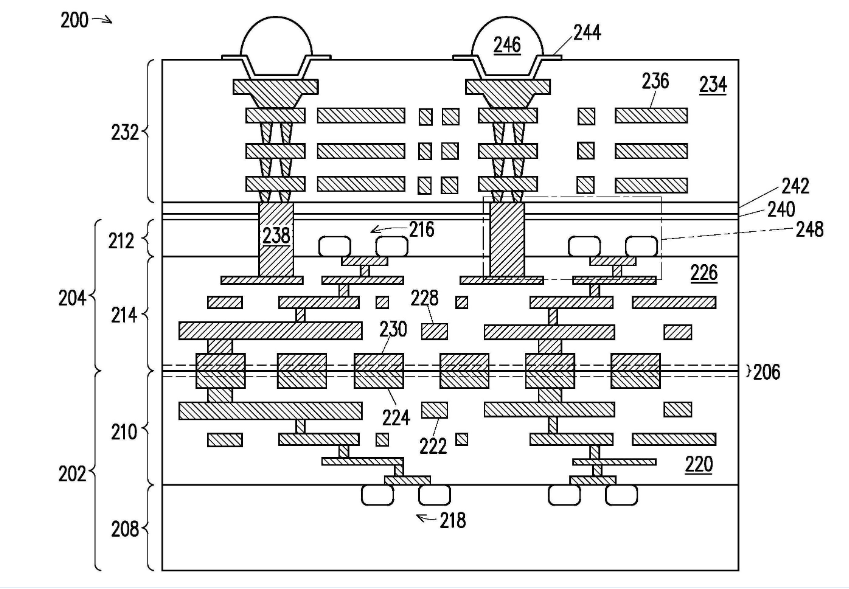

根据专利摘要描述,该专利为一种半导体晶粒封装包括在第一半导体晶粒的组件区上的高介电常数介电层。第一半导体晶粒以晶片叠晶片(wafer on wafer,WOW)型配置方式接合在一起。硅穿孔结构贯穿组件区。高介电常数介电层具有本质负电荷极性,以提供用于调整组件区内的电位的耦合电压。特别来说,高介电常数介电层中的电子载流子吸引组件区中的电洞载流子,此抑制刻蚀容纳硅穿孔结构的凹陷时形成的表面缺陷所导致的陷阱辅助通道。据此,本文所述的高介电常数介电层减少在第一半导体晶粒的组件区中的半导体组件内的电流泄漏之可能性(及/或幅值)。

台积电1月18日召开法说会,公布2023年营收692.98亿美元,新台币营收达2.1617万亿元,年减4.5%。2023年实际资本支出304.5亿美元,其中约70%~80%用在先进制程技术。

(校对/赵月)