如何设计一个射频收发机

在上期的文章中,我们介绍了常见的射频收发机类型和相应的应用场景。那么如何才能设计一个性能优异的射频收发机呢?

一、系统架构

射频收发机设计的第一步是确定系统性能指标,各项指标的需求将直接决定系统架构类型的选择。例如,对于接收灵敏度和抗干扰能力要求较高的卫星通信收发机,选用超外差式收发架构更为合适。该架构中包含的多级高Q值滤波器能有效抑制邻道干扰和电源噪声。再例如,对于蓝牙、对讲机、GNSS(BDS/GPS/GLONASS/Galileo)等窄带应用,选用低中频架构会比零中频更有优势,因为低中频架构能有效规避闪烁噪声的影响。

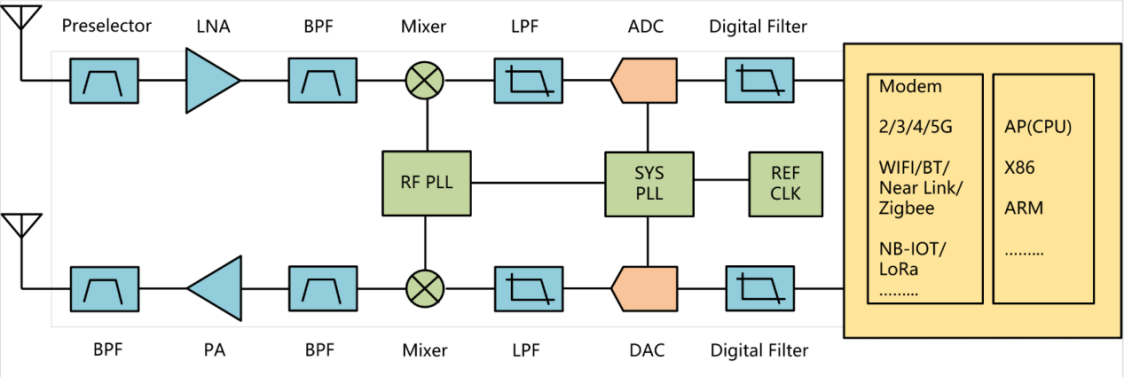

接下来本文将以零中频架构为例,介绍射频收发机的核心性能指标和设计方法。零中频架构具有体积小、功耗低、成本低、便于集成、性能优越等特性,目前占据市场主导地位,广泛应用于Wi-Fi,5G,收音机等。图1为零中频收发机的典型系统架构,它主要由接收机、发射机和频率综合器三部分构成。

图1:零中频收发机架构

二、接收机设计

对于接收机,我们需要考虑的主要性能指标是噪声系数(NF),线性度和增益调整范围。对于零中频架构,还需要考虑系统对于IQ失配和直流偏移的容忍度。

1.噪声系数(NF)

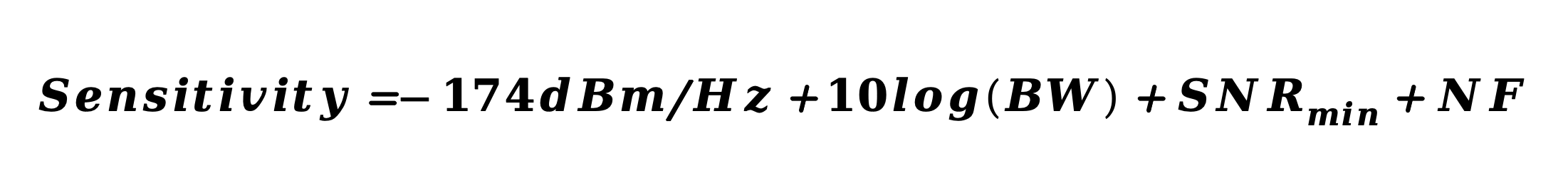

噪声系数的要求可以从系统灵敏度指标计算得到:

其中,-174dBm/Hz为50Ω对应的热噪声底噪,BW为接收信号带宽,为信号解调所需的最小SNR。例如,WiFi的11a/g协议要求误码率不超过10%,在64QAM调制下,对应的为18.3dB。若信号带宽160MHz,灵敏度指标-70dBm,则要求NF<3.7dB。

需要额外注意以下两点:(1)考虑NF指标时不可只考虑接收机自身。前端的射频开关、巴伦等器件的衰减都会造成NF恶化。(2)考虑NF指标时不可只考虑小信号,邻道干扰(ACS)、阻塞等大信号的存在很可能造成NF增大。

2.线性度

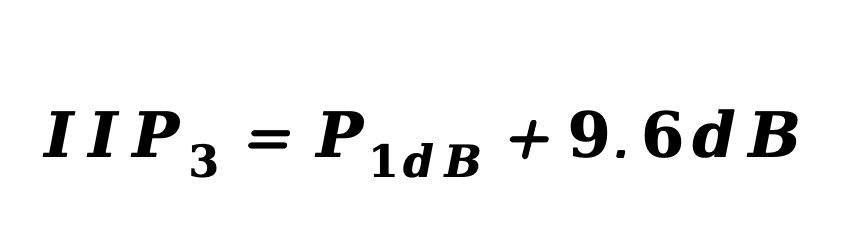

衡量接收非线性特性的常见指标包括1dB增益压缩点(P1dB)和输入三阶互调截点(IIP3)。

P1dB是指接收增益下降1dB时的输入功率,可由接收机最大输入功率得到。例如:接收机最大输入功率-20dBm,信号峰均比9dB,则P1dB至少为-11dBm。

IIP3是指三阶互调功率达到与基波相等时的输入功率。三阶互调的产生有多种情况,通常分为带内IIP3和带外IIP3。前者是指产生互调的两个单音信号处于通带内,后者则指产生互调的两个单音信号处于通带外。需要注意的是,很多资料均会指出P1dB和IIP3之间存在如下关系:

但此公式通常仅适用于带内IIP3。对于带外IIP3,产生互调的两个信号会受到接收滤波器的额外抑制。

3.增益调整范围

接收机通常会根据输入信号功率进行自动增益调整(AGC),以保证ADC输入接近满量程(此时ADC达到最优SNR)。例如:ADC满量程为+10dBm,输入信号峰均比10dB,那么当输入功率从-65dBm增加到-25dBm时,接收增益需要从65dB降低到25dB。

需要注意的是,级联系统的增益等于各级增益之和(单位dB)。当系统从最大增益进行回退时,各级增益的调整策略是一个重要问题。通常优先回退后级增益能最大程度减小增益回退时NF的恶化,但同时必须保证ACS或阻塞存在时,前级不会发生饱和。

三、发射机设计

对于发射机,我们需要考虑的主要性能指标是饱和功率(Psat),线性度,输出功率调整范围,以及IQ失配和输出噪声。

1.饱和功率(Psat)

当发射机最后一级功率放大器(PA)的输入功率增大到某一数值后,再加大输入功率并不会改变输出功率的大小,此时的输出功率即为饱和功率。实际应用中,我们更为关注的通常是最大线性输出功率,即发射机输出的误差向量幅度(EVM)满足系统需求时的最大输出功率。例如:对于Wi-Fi的802.11a协议,最大线性输出功率通常比饱和功率低7~10dB。

2.线性度

在发射机的链路设计中,为了追求更好的线性度,通常遵循两个原则:(1)将尽可能高的增益分配给最后一级PA,以降低前级的输出摆幅和线性度要求。(2)尽可能减少发射链路中的放大级数。

衡量发射机线性度的常见指标包括输出三阶互调截点(OIP3)和CIM3(3rd-Order Counter Intermodulation)。前者是指三阶互调功率达到与基波相等时的输出功率,衡量的是输出级PA的线性度。后者是衡量谐波混频或基带非线性造成的互调影响,存在多种产生机制,在此不做详述。

3.输出功率调整范围

与接收机类似,当发射机的输出功率回退时,同样要注意各级增益的调整策略。如果基带输出保持在较大摆幅,能最大程度减小直流偏移的影响,从而降低本振泄露。但此时,由于需要回退PA的增益,可能会造成PA能量效率的下降。

4.IQ失配和输出噪声

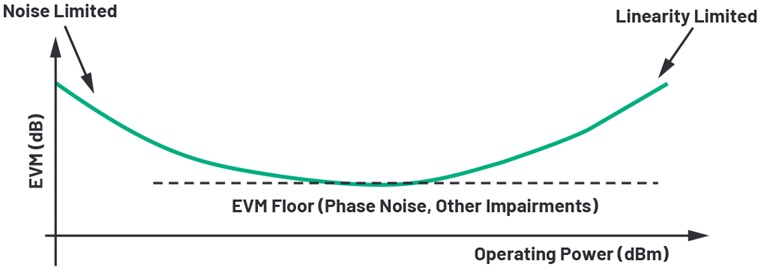

之所以这两个指标放在一起介绍,是因为它们是发射机输出功率回退时影响EVM的关键指标。如图2所示,当输出功率较大时,EVM通常主要受线性度影响。而当输出功率较低时,EVM将取决于输出噪声。在以上两种情况的过度段,EVM会达到最优值,此时EVM主要受IQ失配限制。

图2:发射机EVM随输出功率变化曲线

四、频率综合器

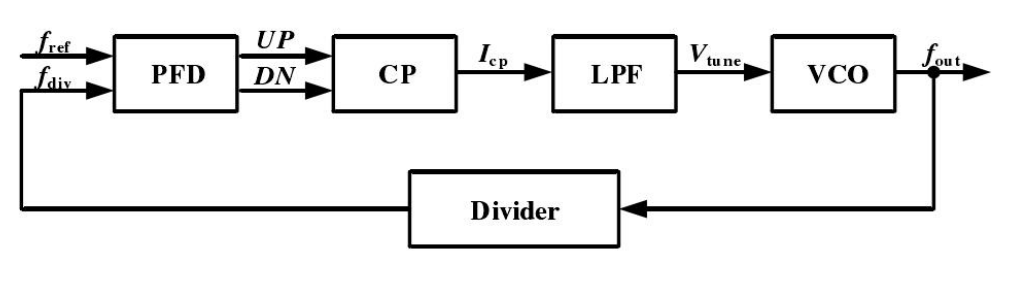

由于具有强大的反馈跟踪能力和对于相噪的抑制作用,Type II锁相环(PLL)成为了当前广泛使用的频率综合器架构。Type II PLL也被称为电流泵PLL,主要由压控振荡器(VCO),鉴频鉴相器(PFD),电流泵(CP),环路滤波器(LPF)和多模分频器(MMD)组成(图3)。

图3:Type II PLL架构框图

1.频率计划

设计频率综合器前,首先要确定频率计划。通信协议规定了频率综合器所需覆盖的频段范围和信道带宽,而应用场景会提出需要支持的外部晶振频率范围。据此,我们将选择合适的VCO数量和MMD分频比的可调范围。

在确定VCO数量时,通常遵循以下规则:单个VCO的频率越高,所需覆盖的频率范围越大,其相位噪声也会越高。但VCO数量的增加不但会加大功耗和系统复杂度,还更容易发生振荡器相互牵引。

2.相位噪声

由于倒易混频(Reciprocal Mixing)的存在,频率综合器的相位噪声会污染接收信号。根据系统对于邻道干扰和阻塞的指标要求,可以计算出对应频偏的相位噪声或对应频段的积分相位噪声指标。

在电路设计中,除了频率综合器中各个组成模块的噪声外,环路滤波器带宽也会极大影响相位噪声。频率综合器的噪声可分为具有低通特性的环路噪声(如电流泵噪声)和VCO噪声。如果系统要求较低的高频(远端)相位噪声,可以选取较宽的环路带宽,从而更好地抑制VCO噪声,反之亦然。

以上仅是简单介绍如何将收发机系统指标转化为模块性能指标的方法。在后续的文章中,我们会继续介绍如何进一步根据模块性能指标的需求选取特定的电路架构,完成收发机设计。

参考文献:

[1]. Behzad Razavi, “RF Microelectronics”, Pearson Education, 2011.

[2]. “Electronic Circuits, Systems and Standards: The Best of EDN”, Newnes_RM, 2016.

[3]. Thomas H. Lee, “The Design of CMOS Radio-Frequency Integrated Circuits”, Cambridge University Press, 2003.

声明:文章来源于地芯科技,版权归地芯科技所有,任何形式的转载或者引用,请与地芯科技联系,并且著名来源。