成电团队在集成电路领域顶尖期刊JSSC上发表研究成果

近日,成电集成电路科学与工程学院智能集成电路与系统实验室在集成电路领域顶级期刊《IEEE Journal of Solid-State Circuits (JSSC)》上发表了其团队在高性能锁相环频率综合器领域的突破性研究成果A Sub-50-fsrms Jitter Fractional-N CPPLL Based on a Dual-DTC-Assisted Time-Amplifying Phase-Frequency Detector With Cascadable DTC Nonlinearity Compensation Algorithm。该项技术实现了一个具有小于50fs抖动的毫米波分数分频锁相环,将毫米波分数分频电荷泵锁相环的品质因数(Figure-of-merit, FoM)推进到了-252dB以下(-252.8dB)。王政教授指导的博士生叶宗霖、耿新林为共同第一作者,王政教授为通讯作者。

研究介绍

随着对数据速率需求的不断增长,近年来通信系统的性能得到了显著提升。作为通信系统性能的关键构建模块,频率合成器如今面临着设计挑战。在无线应用中,由于各种先进的调制方式,频率合成器的抖动要求变得越来越严格。例如,在5G NR n258中,频率合成器的均方根抖动被限制在100飞秒以内。与此同时,高速模数转换器也对时钟抖动具有严苛的要求。例如,在5G赫兹带宽下,具有56dB信噪比的高速模数转换器,需要时钟抖动小于60飞秒。

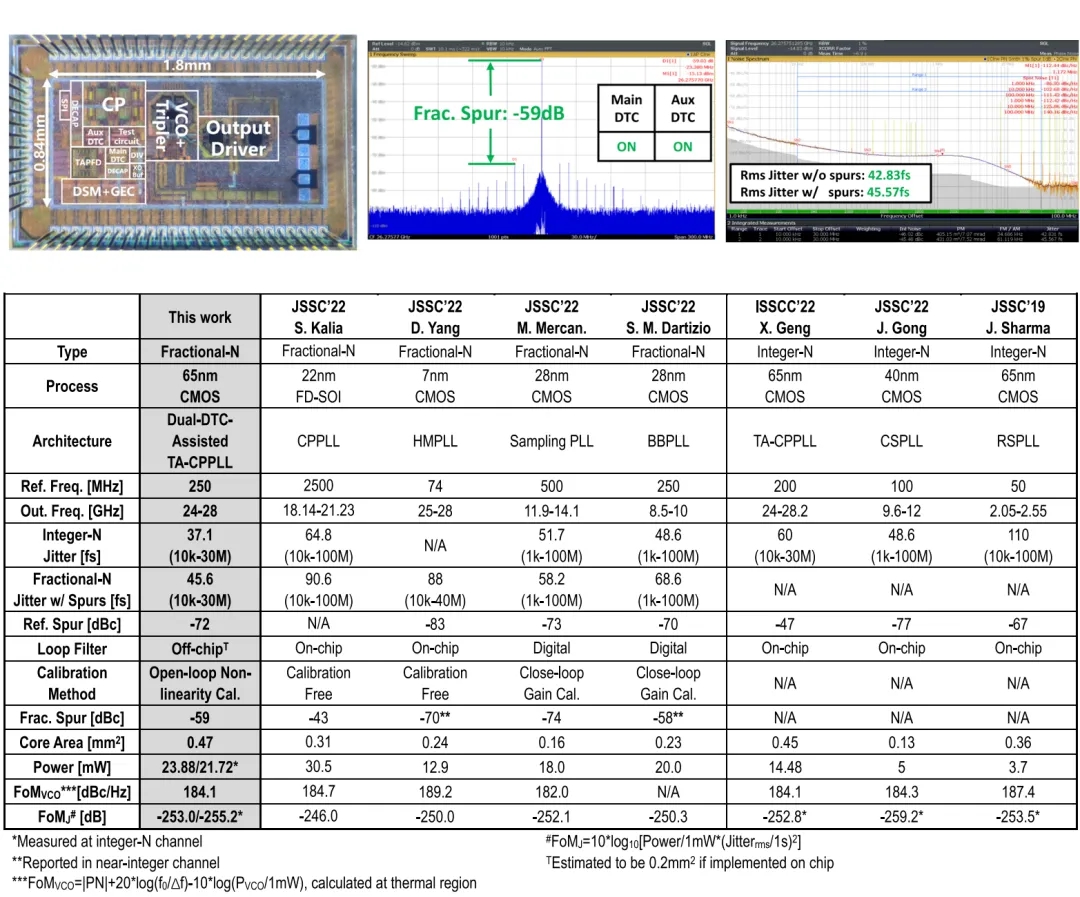

本研究设计了一种24-28 GHz亚50飞秒均方根抖动分数N电荷泵锁相环具有创新性的双数字-时间转换器辅助的时间放大鉴频鉴相器结构,可以在抑制电荷泵的噪声和消除量化误差的同时保持低功耗。此外,本研究还提出了一种可级联的DTC非线性补偿算法,可以大幅度降低分数杂散。所提出的锁相环在整数模式下实现了 37.1飞秒的积分抖动与-255.2 dB 的品质因数,在整数模式下则实现了45.6飞秒的积分抖动与-253.0 dB 的品质因数。

团队介绍

王政教授团队(智能集成电路与系统实验室)面向下一代超高速无线通信、太赫兹成像等应用,长期致力于硅基毫米波太赫兹集成电路与系统的研究,解决晶体管在接近其最高截止频率时面临的一系列挑战,在理论模型层面、设计方法层面、和电路架构层面开展创新性研究工作。团队承担了包括国家自然科学基金重点项目、国家重点研发计划在内的十余项纵向/横向科研项目,多项研究成果发表在包括ISSCC在内的集成电路领域顶级会议和期刊上。近年来指导学生多次获得包括全国大学生集成电路创新创业大赛IEEE杯最高奖等在内的多个奖项。