模拟集成电路教育部重点实验室在模拟集成电路研究的最新成果

继沈易、董志成在IEEE定制集成电路大会(CICC)2023年报告2篇论之后,模拟集成电路与系统教育部重点实验室王夏宇、钟龙杰等在CICC 2024年报告论文3篇。模拟集成电路与系统教育部重点实验室均作为唯一作者单位,向国际同行展示了实验室在模拟集成电路研究的最新成果。

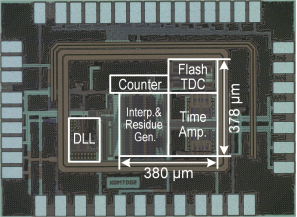

论文一/高分辨率多事件时间数字转换器(TDC)芯片

(第一作者:王夏宇)

论文题目:《A 7.9 ps Resolution, Multi-event TDC Using an Ultra-low Static Phase Error DLL and High Linearity Time Amplifier for dToF Sensors》,本院教师王夏宇为论文第一作者,教育部青年长江学者马瑞和实验室主任朱樟明教授是该文章的共同通讯作者。

直接飞行时间(dToF)激光雷达传感器芯片在无人系统领域具有十分重要的应用前景,而时间数字转换器(TDC)作为制约dToF激光雷达传感器测距性能的关键电路。具有高分辨率、低死区时间特点的多事件TDC电路能够有效消除堆积效应,提高探测精度。传统采用纳特法和多通道交织技术的TDC电路通常难以同时实现高分辨率、低死区时间和多事件量化。实验室提出了一种新型多事件TDC电路架构,采用多级量化和时间放大技术,显著提升TDC分辨率;通过复用信号量化通道现两通道交织工作,有效降低TDC死区时间;结合所提出的超低相位误差延迟链锁相环电路,为第二级粗量化提供低噪声参考时钟信号,提升TDC线性度指标。所提出TDC芯片采用标准0.18μm CMOS工艺,有效面积为0.14mm2,分辨率7.9ps、转换速率80MS/s、动态范围2033.5ns,达到了当前最高的量化分辨率。

图1 所提出的高分辨率多事件TDC芯片

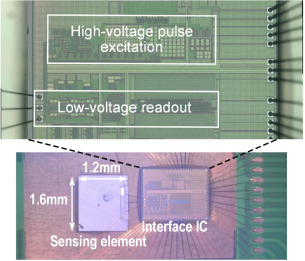

论文二/高分高性能MEMS加速度计芯片

(第一作者:钟龙杰)

论文题目:《A 0.64mm2 Sensor Size, 32.5μg/√Hz Noise Floor, High efficiency MEMS Capacitive Accelerometer using High-voltage Pulse Excitation Technique》,实验室钟龙杰为论文第一作者,教育部长江学者特聘教授、国家优青刘术彬教授和实验室主任朱樟明是文章的通讯作者。

MEMS加速度计芯片领域重要难题之一是噪声与尺寸的约束瓶颈。在微型无人机等电子设备高集成度需求驱动下,MEMS加速度计的尺寸被要求不断缩微,这造成了微机械传感单元的灵敏度显著降低与模拟前端电路噪声等效输入加速度的恶化。为了突破噪声与尺寸的约束瓶颈,实验室提出了一种采用高压脉冲激励读出(HVPE)的解决方案。该方案不仅有效压制了微机械传感单元尺寸缩微导致的噪声恶化效应,还解决了静电力非线性、灵敏度漂移以及高压脉冲可靠性问题。所提出MEMS加速度计芯片采用标准表面硅MEMS工艺与标准0.18μm BCD工艺实现,实测单轴传感单元面积0.64mm2、噪声32.5μg/√Hz、带宽2kHz、单轴功耗80μW。对比国际上最先进的MEMS加速度计的尺寸-噪声性能边界,该工作将性能边界突破并向前推进了2.5倍。

图2 基于所提出HVPE技术的MEMS加速度计芯片

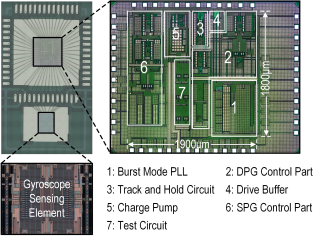

论文三/高性能MEMS陀螺仪芯片

(第一作者:钟龙杰)

论文题目为《A 737nA Always-On MEMS Gyroscope with 5.45ms Start-up Time Using Burst Mode PLL Technique》,实验室钟龙杰为论文第一作者,教育部长江学者特聘教授、国家优青刘术彬教授和实验室主任朱樟明是文章的通讯作者。

快速启动与唤醒是MEMS陀螺仪芯片领域最重要的研究方向之一。微型无人电子系统的姿态控制与惯性导航对惯性测量单元(IMU)的能效有极高要求,通常需要IMU中高功耗的MEMS陀螺仪需要频繁的开启与关闭或者占空比工作来降低功耗,然而MEMS陀螺仪启动时间限制了其占空比工作能力。传统采用低Q值传感单元来降低启动时间的方法,恶化了噪声,不被高精度MEMS陀螺仪所接受;采用Always-on驱动休眠能在不降低陀螺精度的情况下,显著降低启动时间,成为近年来国际主流技术之一。然而基于Always-on驱动休眠的MEMS陀螺仪引入了Always-on驱动功耗与唤醒时间的约束瓶颈,实验室提出了一种采用突发模式锁相环(BPLL)的Always-on MEMS陀螺仪打破了这一瓶颈。所提出MEMS陀螺仪芯片采用标准表面硅MEMS工艺与标准0.18μm BCD工艺研制,实测Always-on驱动737nA、唤醒时间5.45ms,相比于目前最先进的Always-on MEMS陀螺仪(Bosch BMI323),Always-on功耗与唤醒时间分别降低了6.8倍与5.5倍。

图3 基于所提出BPLL技术的MEMS陀螺仪芯片