沐创两篇成果论文再次入选CHES

1.沐创密码芯突破:两篇成果论文再次入选行业顶级会议CHES 2024,截止当前,沐创累计已有五篇文章入选CHES

2.入选论文“A Low-Latency High-Order Arithmetic to Boolean Masking Conversion”在掩码转换安全硬件实现性能与高阶可组合安全性方面实现了突破

3.入选论文“UpWB: An Uncoupled Architecture Design for White-box Cryptography Using Vectorized Montgomery Multiplication”提出了国际首款面向白盒分组密码算法的高效硬件架构

近日,CHES 2024公布了入选论文名单,沐创参与撰写的两篇论文“A Low-Latency High-Order Arithmetic to Boolean Masking Conversion” 和“UpWB: An Uncoupled Architecture Design for White-box Cryptography Using Vectorized Montgomery Multiplication”双双入选,这是沐创在密码安全领域再次迈出的坚实一步。

自成立以来,沐创始终追寻密码安全芯片发展的前沿方向,持续在理论研究、产品研发、性能验证等方面进行投入,不断丰富公司密码安全芯片产品线的同时,积极为行业输出高性价比的产品和解决方案,赋能行业发展。截止当前,沐创累计已有五篇论文入选CHES。

A Low-Latency High-Order Arithmetic to Boolean Masking Conversion

现有研究中,抗高阶侧信道攻击掩码转换算法的硬件实现普遍存在延迟问题,那么如何在实现低延迟方案的同时兼顾安全性呢?该文章给出了答案。

该文章面向低延迟硬件实现,提出了任意安全阶数与转换位宽下通用且软硬件侧信道安全实现兼容的A2B掩码转换算法,突破了现有研究在安全硬件实现性能与高阶可组合安全性方面的局限。

文章贡献度详解

该文章对现有高阶A2B转换结构进行了分析,并对通用参数下侧信道安全硬件实现最少时钟周期进行了评估,由此得出了“高时钟延迟来源于高代数度非线性函数硬件实现中插入的多级抗毛刺寄存器,基于布尔操作的硬件掩码使得多级加法器中的多级进位计算大大增加了转换延迟”的结论。

上述结论的提出是文章的第一项贡献。

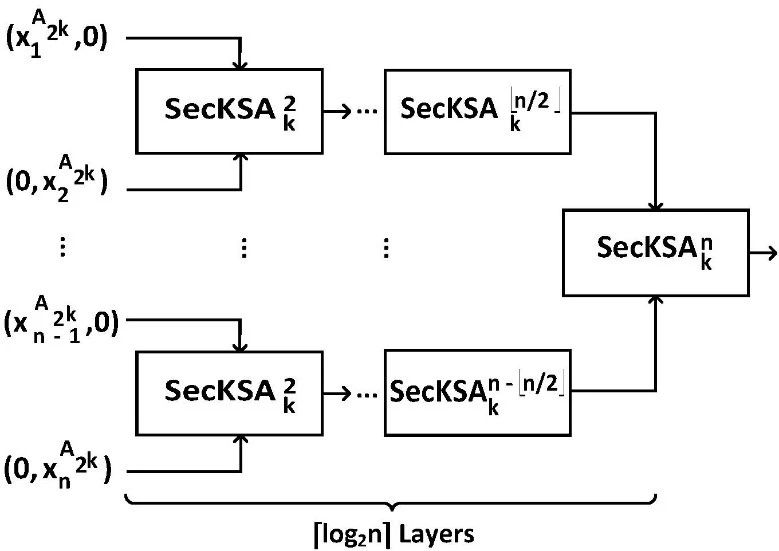

现有研究中基于进位传播加法器的A2B转换算法

该文章在提出兼容PINI与门和HPC与门的侧信道安全无进位加法器的基础上,进一步提出了将中间变量表示为冗余数的A2B转换算法。针对文章提出的改进后的A2B转换算法,我们从理论和实验方向上分别进行了验证:理论角度上,基于理想探针模型和强鲁棒探针模型均证明了任意阶数A2B转换的可组合安全性;实验角度上,采用测试向量评估实验验证得出二阶软硬件实现无一二阶泄露。

该改进后A2B转换算法的提出是文章的第二项贡献。

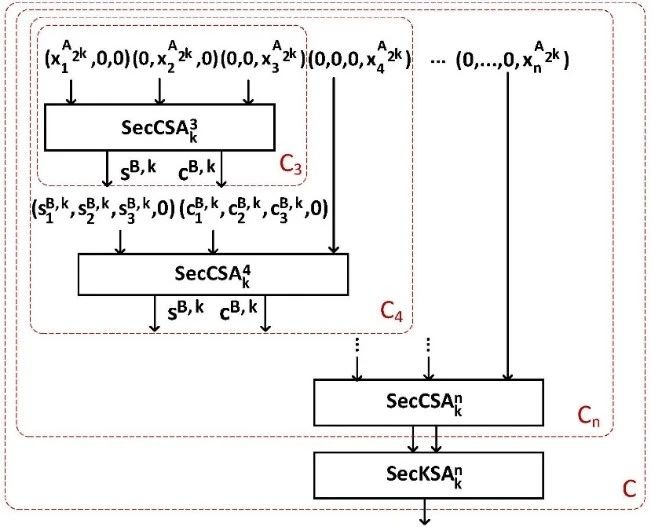

文章提出的基于安全无进位加法器和索引值不变共享值拓展的A2B结构

文章对于不同安全阶数32比特位宽的A2B转换在不同应用场景下的性能进行了评估,其中应用场景包括:FPGA平台、TSMC28nm标准工艺库、PC软件实现等。评估结果显示:基于改进后的A2B转换算法,二阶硬件实现时钟周期延迟减小了42%,软件速度提升了30%。由此可将改进后的A2B转换推广到B2A和素数模应用场景。

上述评估结果的提出是文章的第三项贡献。

32比特位宽A2B转换不同安全阶数下时钟周期延迟对比

UpWB: An Uncoupled Architecture Design for White-box Cryptography Using Vectorized Montgomery Multiplication

白盒密码小科普

Q:什么是白盒密码模型?

A:白盒安全模型指的是攻击者对密码算法的执行环境有完全的访问和控制权,例如观察和分析软件代码的数据流、地址流以及内存中的内容。

Q:白盒密码的目标是什么?

A:白盒密码学的理想目标是在白盒安全模型下也能保护设备中运行的密码算法的密钥。

Q:白盒安全模型的优越性有哪些?

A:相较灰盒和黑盒安全模型,白盒安全模型被认为是一种安全性更强的安全假设,同时白盒安全模型也与实际应用场景更紧密贴合。

研究现状

基于不可压缩性(incompressibility)或空间硬度(space-hardness)安全概念而设计的新的白盒分组密码算法是目前比较流行和具有前景的技术路线之一。但该路线也存在明显的短板:尽管能够提供可证明的安全性,但新的白盒密码算法带来了较大的计算开销,在传统CPU上的运行性能远低于传统的分组密码算法,从而限制了白盒算法的广泛应用。

上述问题从近年来发表在ASIACRYPT、CHES会议上的成果论文中就可窥见,论文中采用了嵌套的置换网络(NSPN)结构来构建新的白盒密码算法,其性能受到巨大的轮数、嵌套的数据循环等算法特点的限制。

论文详解

● 文章创新性

本文章创新性地提出了国际首款面向白盒分组密码算法的高效硬件架构,该架构可支持流行的白盒分组密码算法,包括SPNbox-8/16/24/32, Yoroi-16/32, WARX-16三种系列算法的加解密模式。

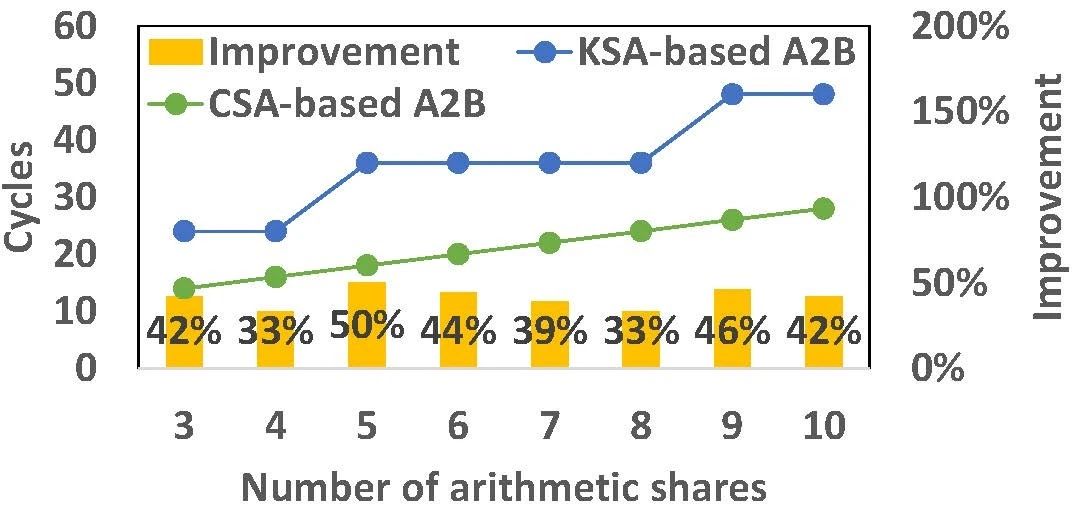

白盒密码在基于云的数字版权管理的应用。白盒密码黑盒模式的硬件加速器被部署在服务器端,而白盒密码白盒模式的软件实现被部署在客户端。

● 文章贡献度

该文章工作在时序调度、算法层和硬件实现层分别提出了相应的优化方法。

★ 时序调度方面:该文章提出了细粒度任务划分方法,以有效解耦嵌套的数据循环,结合利用多层次计算并行性,有效提高了白盒分组密码算法的运行吞吐量;

★ 算子硬件优化方面:(1)基于优化后的蒙哥马利算法设计了灵活的向量化模乘单元,能够处理多种数据位宽、多尺寸矩阵向量乘法以及不同的不可约多项式;(2)基于主对角线数据流结构设计了可配置的矩阵向量乘法器,从而实现随机的多维度MDS矩阵的高效处理;(3)基于矩阵的加性和乘性分解设计了紧凑统一的多尺度列混淆硬件单元,并采用后向启发式搜索方法定制化设计了常数乘法器。

● 性能优越性

在TSMC 28nm工艺下对文章提出的硬件架构进行了DC综合评估。与运行在桌面PC上并采用AES-NI和AVX指令优化后的软件实现相比,该架构的平均吞吐量取得了约91倍的加速,而单个算核面积消耗约0.14mm²。