浙江大学集成电路学院卓成等在《Nature Communications》发文报道首个基于铁电存算芯片的组合优化求解器框架

组合优化问题在现实生活中具有广泛的应用场景(如物流、资源分配、金融、交通)。这类问题通常属于非确定性多项式时间难题(NP-hard),具有极高的计算复杂度。目前,基于传统冯·诺伊曼体系架构的组合优化问题求解器的芯片尺寸、成本随问题规模呈指数性增长,性能和求解能力则指数性下降,因此亟需探索更加高效的组合优化问题专用芯片,这也是美国国防部去年发布的2.38亿美元微电子计划重点方向之一。

近日,浙江大学集成电路学院卓成教授团队联合国际合作单位在《Nature Communications》期刊在线发表了题为“Ferroelectric compute-in-memory annealer for combinatorial optimization problems”的研究论文,报道了首个基于铁电晶体管存算一体芯片的组合优化问题求解器软硬件协同设计方案。

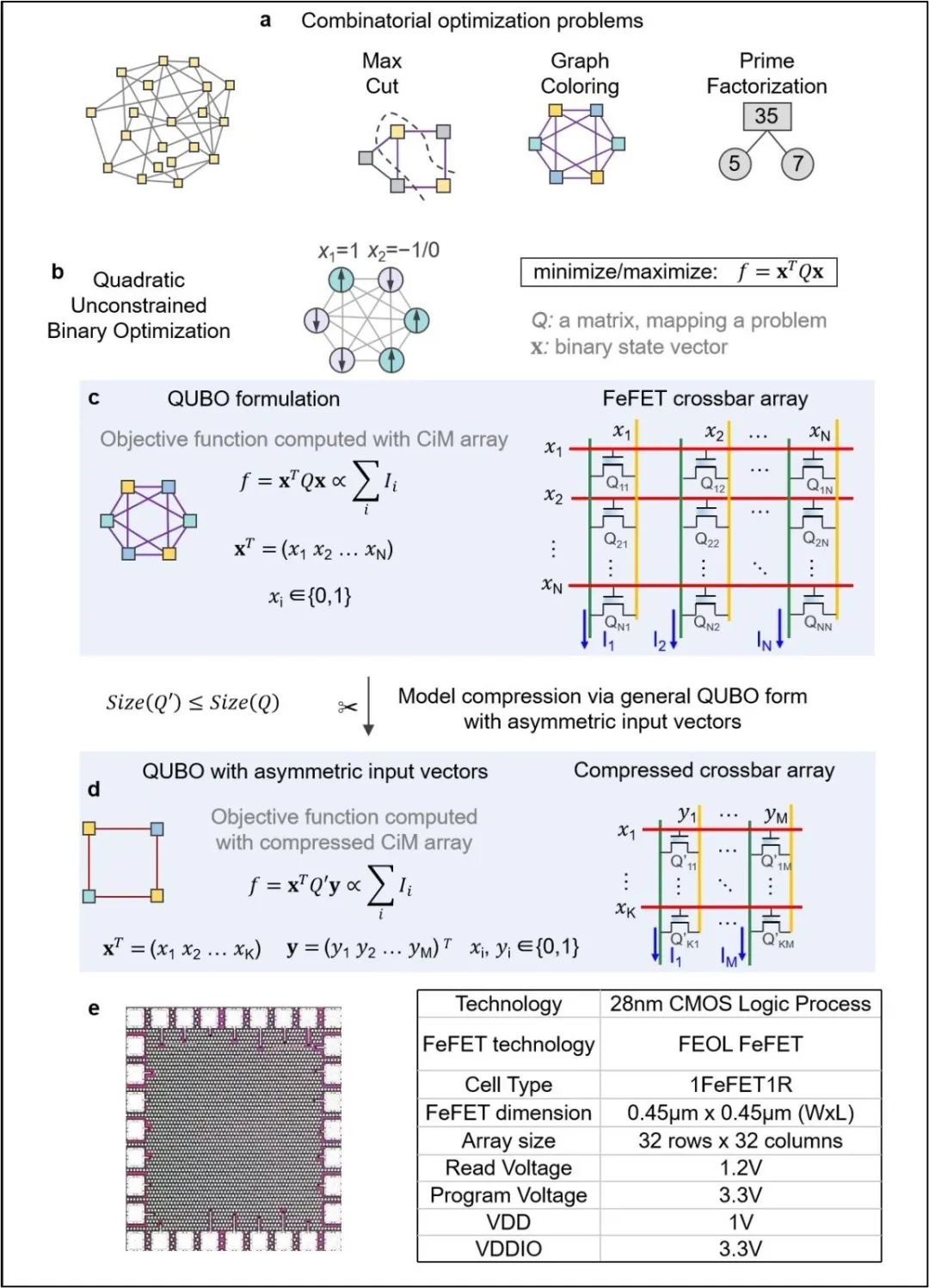

团队论述了多类组合优化问题(如最大割问题、染色问题、质数分解问题)的目标函数到二次无约束二值优化形式(QUBO)的转化方法,设计制备了1kb规模铁电基存算一体阵列,充分结合铁电晶体管单器件三输入的与门逻辑特性,从芯片层面实现了QUBO的向量-矩阵-向量乘法核心运算的单步加速,大幅提升了求解器运算性能;此外,团队根据铁电晶体管三端口结构,提出了针对目标函数的QUBO矩阵无损压缩策略及其对应的非对称性输入向量和矩阵权重映射方法,大幅降低求解所需硬件规模;最后,在存算芯片加速QUBO单次迭代的基础上,提出多周期模拟退火算法,高效实现了问题求解的整体质量和速度。

图1 基于铁电存算一体芯片的组合优化求解器框架

团队这一软硬件协同设计的求解器框架,节省了75%的芯片开销,相比传统求解器求解速度翻倍,解质量提升27%,大幅强化了组合优化求解器的求解规模和求解能力。这一工作为后续更大规模、更高效以及更普适的组合优化专用芯片硬件提供了研究基础。