积蓄本土EDA发展能量 芯易荟专注“实用”解决行业痛点

集微网消息,EDA(电子设计自动化)软件是半导体产业的“芯片之母”,在半导体制造、设计、封测等产业环节的仿真、验证等流程中都扮演着关键作用,但其在整个产业链中是壁垒极高的存在。近年来,伴随着中国EDA市场迅速增长、国外技术出口设限,国产替代迎迫切发展机遇,国内也涌现出一批新生力量,EDA新锐芯易荟(ChipEasy)表现亮眼,以强势自研技术推动本土EDA发展。

今年4月,芯易荟正式发布了一款以C语言描述,基于RISC-V指令集架构的EDA工具“FARMStudio”,主要针对密集计算和复杂数据处理的应用场景。对于这一工具推出的背后故事及市场布局、市场现状等,集微网有幸采访到了芯易荟公司创始人汪人瑞(Albert Wang)及CEO汪达钧(Bill Wang)。

结合传统软硬件优势 加速定制化处理器IP

为了满足产品需求及市场,越来越多企业开始选择自主开发SoC芯片。在芯片设计过程中,IP化让设计灵活而快速,也是芯片设计敏捷化的唯一道路。与此同时,芯片设计中同质化设计较多,公司需要定制化方能建立有竞争价值的IP和系统设计。因此,定制化IP成为目前市场的主流趋势。

芯易荟创始人汪人瑞认为,定制化IP里定制处理器是最大类之一,也是发展最快的一类。他举例说明,“像GPU、GPGPU、TPU、DPU、VPU……形形色色的PU均是定制处理器,而前面的字母则是定制。顺应定制化IP市场趋势,FARMStudio的设计理念是,基于处理器加上定制指令进而实现多快好省的设计,这也是我们开发这款工具的初心。”

除了基本设计理念,汪人瑞还从更深层次进行解释:传统软硬件具有不同优势,软件具有高灵活性,硬件可实现高运算效率,但两者优势互斥,无法同时实现。FARMStudio推行的FARM(Flexible Advanced RISC Machine)设计方法学就是把运算效率和设计效率有机结合,即将上层软件到底层硬件的每一步的算法设计全部融合,真正实现处理器软件和硬件的一体化设计,让算法、软件、硬件、验证工程师能够在同一个开发环境里根据应用需求快速定制开发产品。

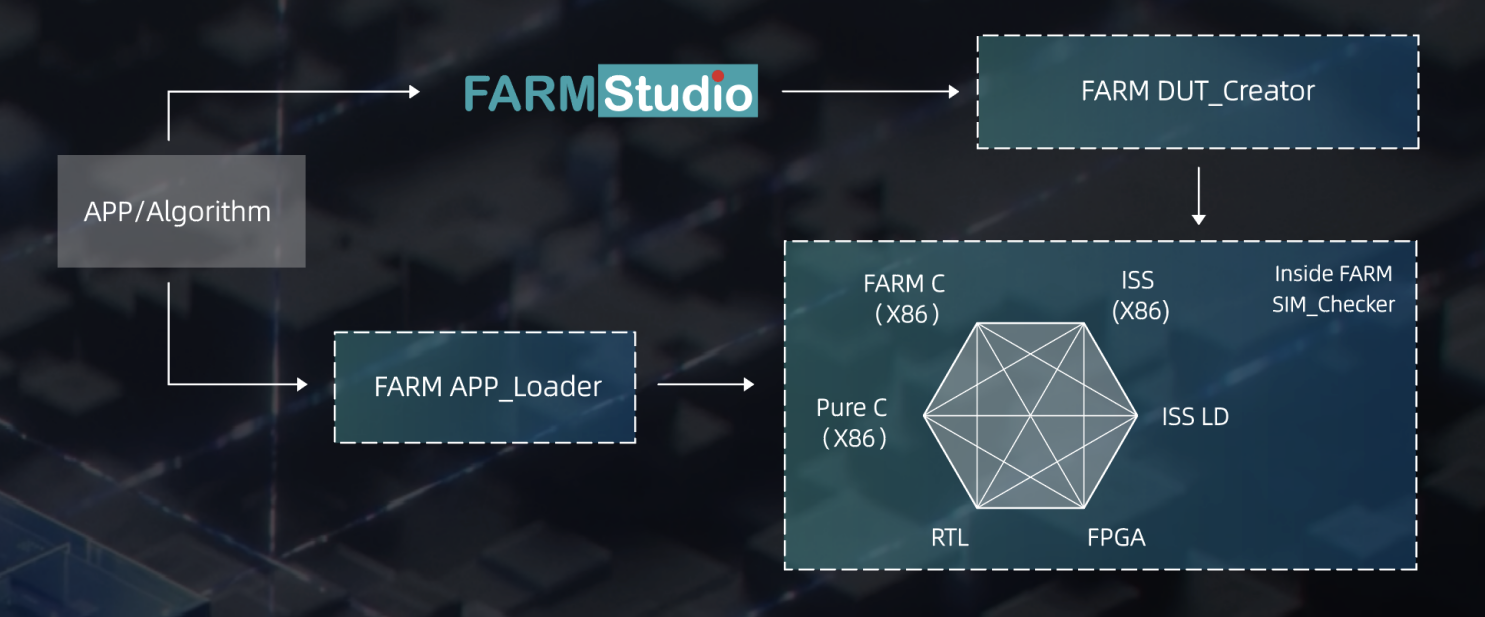

而FARMStudio的推出,也让这一理念得以实现与有所突破。FARMStudio拥有开源的RISC-V基础指令、FPGA云开发测试环境等多项技术优势,特别值得一提的是拥有全球首创的多层次验证环境,实现了从C语言代码到指令级的周期精确仿真,到FPGA上的仿真,再到电路的RTL仿真等多个层次的相互验证。

汪人瑞指出,传统系统设计环节中的验证复杂而繁重,因为传统设计环节中软件和硬件的验证方法完全不同。而如何将从软件到硬件的验证做到一致,做到方便,做到高效便是芯易荟试图解决的问题之一。“芯易荟推行的就是把‘从软件到硬件验证方式不同的鸿沟’填满,让客户自然流畅地从系统到软件、指令、电路逐步地细化及验证,以简化系统设计逐步优化的任务和负担,这是使用传统设计方法和工具所无法做到的事情。”

据了解,FARMStudio的推出目前主要面向两大应用:一是面向数字运算;二是面向运算密集型应用,如音频处理、视频处理、AI、计算机视觉、IoT等应用场景,可实现跨多个行业的运算需求。

对于后续FARMStudio的升级及拓展,芯易荟CEO汪达钧表示,首先在应用层面会持续拓宽,如后续会支持TinyML等特殊算力需求的应用;其次是技术深度不断加强,例如运算效率是非常重要的一点,将通过工具不断提升MAC的利用率,同时降低功耗,达到单位面积的算力最高及功耗最低的目的。

三大定制化IP展示 多方位解决设计难题

FARMStudio发布半年多以来,不断有客户通过FARMStudio进行IP定制化设计,汪达钧表示,本次ICCAD芯易荟将对这些定制化IP进行demo展示,包括DSP32的灵活的指令开发、DSP32优秀的浮点性能以及在ORB算法中可加速复杂指令设计等,向观众全方面展示FARMStudio这一工具的核心优势。

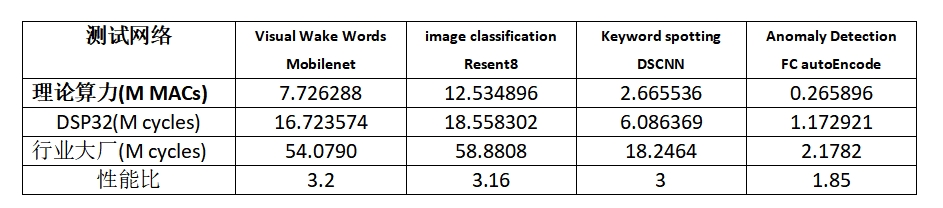

在DSP32的灵活指令开发demo中,演示了在加入SIMD的定点指令后,DSP32计算resnet8网络的推理性能快速得到了提升。resnet8包含了卷积、残差、激活等多个主流神经网络算子,在算子转换成定点计算后,在DSP32上可以针对性采用VLIW和SIMD的方式对计算进行加速。

得益于神经网络量化的优势,可以在不改变DSP32的架构情况下,使用FARMStudio高效地增加SIMD指令,在原先float指令基础上,提高处理性能。主要表现为:

并行处理能力: SIMD指令能够同时处理多个数据元素,有效地利用了硬件资源;

编程简化: 使用intrinsic的方式,能够更容易地实现C代码,减少了编程的复杂性;

能源效率:降低功耗,提高能源利用效率。

汪人瑞特别指出,利用FARMStudio工具灵活增加SIMD及VLIW指令后,DSP32运算单元计算利用率在60%以上,甚至可以达到80%,这是这一工具的优势和竞争力所在。

在浮点运算方面,FARMStudio表现同样出色。浮点运算由于可以提供的更大动态范围和精度,因此成为多种信号处理算法的一项要求。芯易荟定制化IP--DSP32拥有优秀的浮点性能,具体表现如下:

浮点性能提升主要拥有两大难点,一是如何将浮点运算做快做小,降低硬件成本,提高运算效率;二是如何提高运算精度,因为多次运算容易累积更多误差。对于难点的处理,汪人瑞称:“首先芯易荟定制的浮点运算跟行业标准比起来要快很多,甚至可以快一倍,而且硬件成本低。其次,降低误差方面,在基于标准浮点运算指令之上,芯易荟拥有专利化的附加指令,使浮点运算在同行业内性价比领先。”

芯易荟表示,DSP32优秀的浮点性能主要来源于两个方面:

采用VLIW微架构和低延时的浮点计算单元:VLIW架构能够并行执行多个指令,在大量并行任务的场景中,VLIW架构的DSP32表现更为出色。低延时浮点MAC微架构可以灵活地将不同计算合并在同一计算单元。

优秀的编译器:在代码编译阶段就已经对指令进行了分析和优化,将可以并行执行的指令打包成一个指令包。这样,在CPU执行指令时,就可以同时处理多个指令包,从而提高了CPU的效率。

此外,芯易荟还列举了FARMStudio在加速复杂指令设计方面的应用。ORB是Oriented Fast and Rotated Brief的简称,可以用来对图像中的关键点快速创建特征向量,这些特征向量可以用来识别图像中的对象。ORB算法在计算机视觉领域具有广泛的应用,其特点是速度非常快,而且在一定程度上不受噪点和图像变换的影响,例如旋转和缩放变换等。

汪人瑞认为,ORB是典型的运算密集型应用,FARMStudio在此可以发挥最大作用。具体表现在:工具易用,传统Verilog开发流程需要6人在1年的时间才可完成,而使用FARMStudio后,1位工程师在2个月即可完成;工具的使用方法高效,使用容易;应用方面没有局限性,从简单指令到非常复杂的指令都能使用,从而达到最佳的PPA或性价比。

专注“实用”而非“超越” 真正解决行业痛点

目前,我国国产的EDA工具发展很快,但是与国际巨头如Synopsys、Cadence和Mentor相对差距仍然很大。汪达钧表示,“本土EDA工具正处于转折的关键时期,随着行业进入了后摩尔定律时代,本土EDA应加快技术沉淀和市场推广,助力行业的蓬勃发展。”

他认为,今后的20年是大数据的时代,如果没有算法及算力把这些数据进行处理,数据是没有价值的。所以行业下一个10年甚至20年所要面对的挑战是,算法到算力的实现,即有效率地降低设计成本和周期。

对于未来国产工具的发展,汪达钧表达了自己的期望,“挑战之下,国内EDA工具厂商应当更好的通过自主创新,为芯片设计行业带来更有价值、更具有独特性的技术方案,提供优质、可靠的产品和服务。真正解决未来20年将遇到的痛点问题,而不止是单纯的‘替代国外巨头’这样的目标。”

汪人瑞对于这一话题也做了补充,他表示行业的痛点就是到了设计方法学必定要更新的时代,目前的方法学已经老旧,摩尔定律发展变慢,已跟不上市场需求的发展,方法学的改变是一个挑战,也是机遇。“最重要的是,企业不要说要超越谁,而是真正解决了什么问题,对客户贡献了什么价值。这是我对国产EDA工具发展最大的期待。”

写在最后

2023年11月10日-11日,中国集成电路设计业2023年会(ICCAD 2023)将在广州保利世贸博览馆举办。届时,芯易荟将携FARMStudio工具,工具背后的FARM设计方法学,以及ORB算法应用、定点运算、浮点运算等DEMO进行现场展示与讲解,欢迎大家莅临!

地点/展位号

广州保利世贸博览馆

05-06、55-56、65-66、115-116

(校对/孙乐)