770亿晶体管的挑战:如何让汽车SoC耐用15年?

由于终端智能化水平越来越高,作为系统核心,SoC的集成度和规模也愈发庞大。同时,终端系统中包含的芯片数量也在成倍增加,系统复杂度的提升加大了SoC的运行挑战。

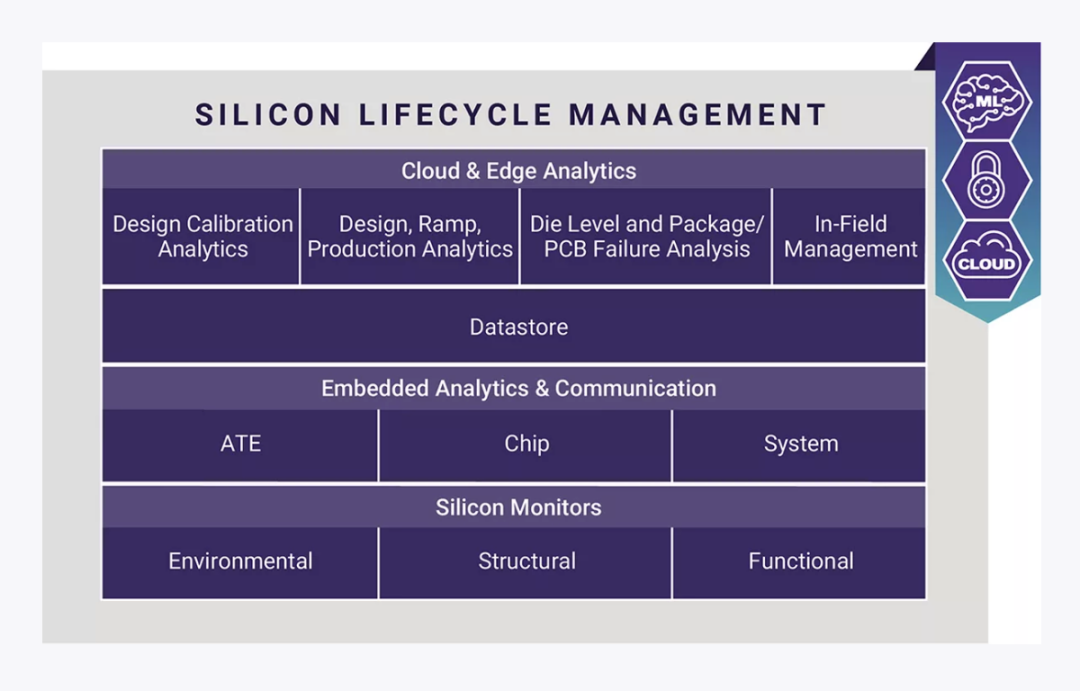

这一情况在汽车市场最为突出,车规级芯片主要用于安全和关键任务应用,从设计到部署的整个周期里,需要有功能和性能监控来应对汽车SoC的功能安全和网络安全等问题。因而,新思芯片生命周期管理(Silicon Lifecycle Management)成为优化复杂芯片的关键手段,让这些芯片能够在汽车、数据中心、工业控制等实际工作场景中运行更长的时间,应对日益增长的设计成本挑战的同时,满足实际工作环境下的功能和性能要求。

作为全球排名第一的芯片自动化设计解决方案和芯片接口IP供应商,同时也是信息安全与软件质量的全球领导者,新思科技提供集成多个产品和功能的芯片生命周期管理(SLM)平台,提供从芯片到系统的深刻洞察力。

当前,芯片生命周期管理(SLM)所提供的功能正逐渐被集成到芯片设计中,在整个芯片生命周期内,尽可能多地收集数据,从而改善芯片和系统的可靠性和运行表现。

从设计到应用,可靠性挑战日益严峻

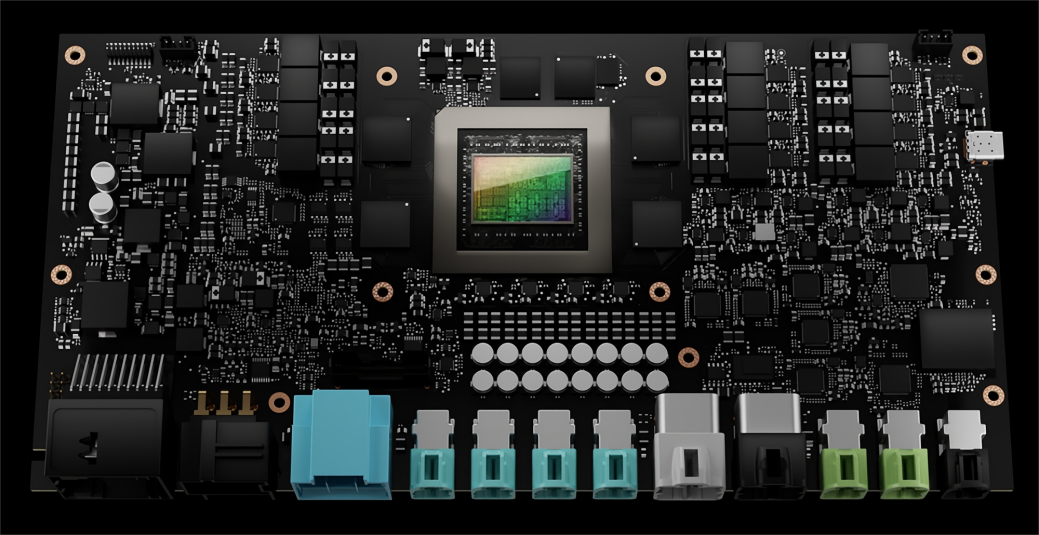

研发人员正尝试将更多样的功能融入到一颗芯片中,以实现更高的集成度和效率,芯片复杂度也随之上升。这个复杂度体现在很多维度上,包括先进的工艺让单颗芯片里面有数百亿、上千亿的晶体管数量;异构集成的架构让芯片成为AP、BP、NPU、ISP等功能单元的集合;同时,承载这颗芯片运转需要一个复杂的PCB系统。以英伟达DRIVE Thor芯片为例,它是一颗能够提供2000 TOPS算力的车规级SoC,内建晶体管数量达到770亿个。如下图所示,为了释放DRIVE Thor芯片的性能,DRIVE Thor的设计非常复杂。

图 1:基于英伟达DRIVE Thor的系统(图源:英伟达)

然而,只是完成芯片设计和系统设计是不够的。在实际应用场景中,可靠性和安全性保障有时候比性能更重要,尤其是在汽车驾驶场景中,从功能实现、车规级认证,到系统实现和现场应用,所面临的挑战贯穿了芯片从设计制造、测试乃至实际工作场景的整个生命周期。

在功能实现方面,高级辅助驾驶(ADAS)和自动驾驶功能升级对芯片的要求越来越高,就像上述提到的英伟达DRIVE Thor芯片,基于台积电4nm工艺,内部晶体管数量超过700亿,这让芯片对制造工艺缺陷是非常敏感的。

与此同时,先进的自动驾驶芯片还会采用2.5D/3D封装和Chiplet技术来构建异构计算体系,在汽车E/E架构集中化发展过程中,这种异构计算体系非常重要。为了减少ECU用量,只是芯片集成度提升还不够,芯片本身还要能够提供虚拟机等软件技术,再加上承载自动驾驶算法,整体上实现了基于软硬件融合的边缘计算大系统。

为了实现这些功能,芯片必须满足特定的行业标准。车规级是一项比消费级和工规级更严苛的标准,要求芯片在设计之初就将车规级标准纳入其中,以确保功能安全。车规级芯片的使用寿命要求一般是15年;AEC-Q100用于可靠性测试,其中0级耐温要求是-40℃~+150℃;ISO26262是芯片功能安全认证,安全气囊、防抱死刹车、动力转向等系统需满足ASIL D等级。在这些严苛的标准下,冗余设计所带来代价非常高昂,需要考虑的因素也非常多。

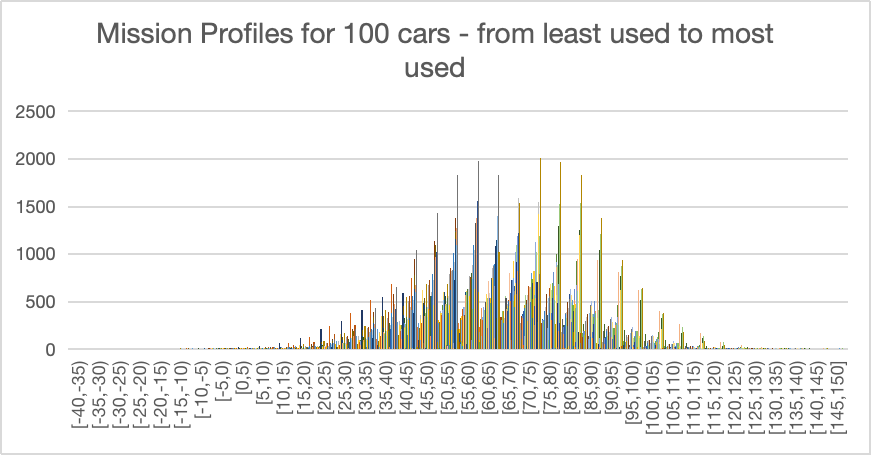

以芯片使用寿命为例,对于电动汽车而言,驾驶只是其中一个场景(预设平均每天驾驶时间约为2-3小时),还有相当一部分使用寿命消耗在充电场景下。一般情况下,这个时间消耗很容易超过4万小时。因而,如下图所示,车规级芯片在15年的寿命周期内,运行时长可能会高达13万小时。很多车规级芯片还会有被过度使用的预期,通常设计寿命是标准寿命的两倍以上。

图 2:电动汽车运行时间的可能性分析

冗余设计还需要考虑未来汽车功能的升级,OTA升级已经成为智能汽车提升竞争力的必要手段,这需要在芯片设计时留出足够的空间和灵活性,以支持后续的功能升级。

AEC-Q100和ISO26262等认证保证了车规级芯片设计的基本要求,但相应的挑战仍然在不断涌现,由芯片设计转为系统设计和现场应用。系统设计层面,自动驾驶芯片要想正常工作,一方面要为各种传感器和数据流留出足够的接口,另一方面需要配套复杂的外围电路,包括电源、接口和隔离保护等。系统中提供不同功能的元器件的老化曲线是存在一定差异的,这也会带来整体系统可靠性和安全性方面的挑战。

最后的挑战来自现场应用。在如此漫长的运行周期里,尚未完全测试的物理环境很可能会突破车规级芯片的可靠性极限,包括高温、应力等。以高温为例,当前越来越多的地方开始出现历史性极值的高温天气,使得车规级芯片可能持续工作在一个不利于散热的高负荷环境中,这很明显会进一步加速芯片的老化,甚至导致在产品生命周期内出现功能失效的情况。

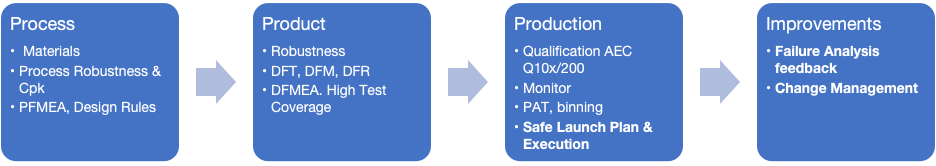

为提升车规级芯片在设计、制造、部署和使用过程中的可靠性和稳定性,汽车电子委员会(AEC)零缺陷(Zero Defect)框架推出了AEC-Q004,这套标准允许芯片供应商能够在最佳实践列表中进行选择,以持续改进芯片设计的各个关键环节,可以有效地确保汽车电子产品在高温、低温、湿度、机械振动和电磁干扰等各种极端条件下的稳定性和可靠性,从而实现终端产品零缺陷。

图 3:汽车零缺陷框架示例

重要的话讲三遍,芯片和系统的复杂度正在显著提升,要满足AEC-Q100和ISO26262认证,以及AEC-Q004零缺陷框架,进而让车规级芯片在整个生命周期内都具有出色的可靠性和安全性,IC从业者所面临的挑战越来越大。需要一种新方法来监测如何开发、操作和维护基于硅的系统,芯片生命周期管理(SLM)所提供的功能变得不可或缺。

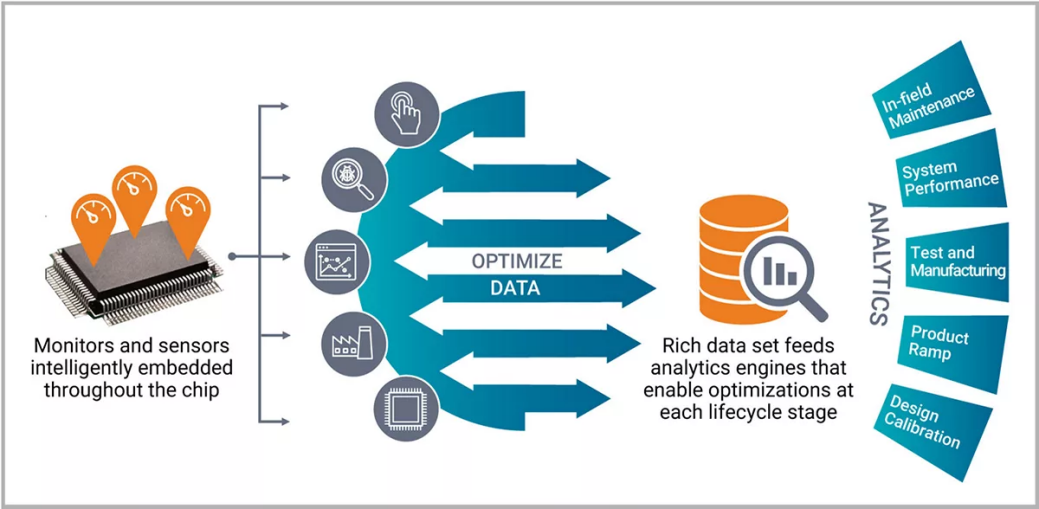

芯片生命周期管理(SLM)是一种基于大数据管理芯片的流程,数据来源于工艺/电压/温度(PVT)传感器、可测性设计(DFT)和内置自测试(BIST)资源、结构和功能监控器、嵌入式片上分析。基于以上产品和解决方案,芯片获得的信息会被传输至某个特定位置,进行进一步的分析、控制和优化。

图 4:芯片生命周期管理(SLM)数据来源

芯片生命周期管理(SLM)将成熟的芯片测试基础架构、经过验证的IP、供应链安全、芯片生命周期管理方法和生态系统平台等结合在一起,让芯片的设计、制造和使用变得更加稳健,主要优势包括:

实现更优的PPA设计

快速提升制造良率

缩短芯片上市周期

优化系统的功耗和性能

提升现实应用中的可靠性和稳定性

需要特别指出的是,芯片生命周期管理(SLM)对研发下一代芯片很有帮助,能够让设计人员清晰地了解这一代芯片在早期边际退化、离群值检测和故障预测时具体发生了什么。

芯片状态检测和结果分析是芯片生命周期管理(SLM)重要的组成部分,这种检测和分析跨越了芯片整个生命周期,可以持续探索硅性能的边界,为下一代芯片设计研发做好准备。

图 5:硅状态检测和修复的边际分析

新思科技提供领先且完备的芯片生命周期管理(SLM)平台

芯片生命周期管理(SLM)是一个相对较新的、基于大数据的设计和部署管理流程,能够在整个芯片生命周期内获取和分析数据,并提供可操作的见解。考虑到产品全生命周期数据来源和平台构成,就会发现实施产品全生命周期管理具有一定的门槛,越是复杂的SoC和系统,这个门槛越高。

为了帮助设计人员更好地部署、实施产品全生命周期管理平台,并从中持续获得可操作性的见解,新思科技提供集成多个产品和功能的芯片生命周期管理(SLM)平台,与新思科技全面的EDA工具和领先的IP方案相结合,帮助开发人员应对复杂芯片在开发和部署等方面的挑战,以实现最佳的硅成本、质量、健康和性能。

如下图所示,新思科技芯片生命周期管理(SLM)平台能够帮助了解芯片在每一个阶段的操作指标,不仅是芯片自身,还包括嵌入式环境、系统架构和功能监测器,收集相关数据并进行持续的分析。片上部署的监控电路不仅可以从ATE、芯片和系统中获取数据,并将数据发往片外,还可以被系统级测试捕捉,甚至是传送到云端。这些数据最终被保存在相同的数据库中,云分析技术和嵌入在片内的AI引擎将会根据这些数据持续提供可操作的优化建议。

图 6:新思科技芯片芯片生命周期管理(SLM)平台

从产品层面来看,新思科技芯片生命周期管理(SLM)平台包含了监视器IP、传感器IP、设计分析、产品分析、现场分析、智能数据提取和系统性能优化等丰富的产品组合。其中,SLM IP又可以细分为PVT监视器IP、PMM监视器IP、时钟和延迟监视器IP、UCIe监视器IP和各种高速访问和测试IP等。

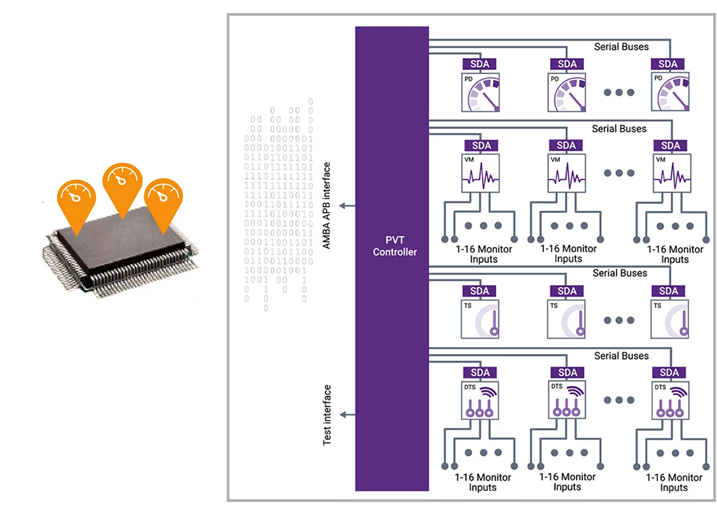

这里主要解读一下PVT监视器IP。PVT监视器IP负责工艺、电压和温度,可以跟踪片内局部电源电压的动态波动,直接测量硅温度来检测芯片上的局部热点和冷点。新思科技PVT监视器IP覆盖28nm到3nm工艺阶段,可以帮助这些芯片实现最佳的PPA平衡,以带来显著的性能和可靠性优势,典型案例包括自适应电压调节(AVS)和动态电压与频率方案(DVFS)等。

目前,新思科技PVT监视器IP已经经过SGS-TÜV Saar认证,满足ASIL-B功能安全等级,符合AEC-Q100 2级标准,可以用于复杂的汽车芯片设计。

图 7:PVT监视器IP部署

在设计和产品分析方面,Avalon软件系统是用于故障分析、设计调试和低成品率分析的下一代CAD布局和故障隔离标准,能够促进产品/设计团队和FA(故障分析)实验室之间更紧密协作。新思科技的SysNav将Avalon的能力进一步扩展到了封装系统,可应用于PCB、多芯片模块以及堆叠式芯片应用。

借助Avalon软件系统和SysNav,开发人员可以优化芯片质量和良率,并改善板级的产品缺陷检测和设备调试。此外,在设计方面,新思科技芯片生命周期管理(SLM)平台还提供TestMAX和Fusion Compiler RTL到GDSII解决方案,以及Fusion Design Platform等,帮助开发人员基于硅数据来优化设计。

当芯片部署到现场应用之后,新思科技监视器IP和传感器IP将继续发挥作用,这些数据可以被芯片上的AI引擎以及云分析技术快速处理,实时分析和优化系统方案,并提供预测性维护、老化识别和故障检测等功能,不仅能够降低功耗、延长设备生命周期,还能够提供贯穿整个设备生命周期的可追溯性。

借助新思科技芯片生命周期管理(SLM)平台,上述提到的汽车芯片的设计和部署挑战都会迎刃而解。当然,这些芯片生命周期管理(SLM)方案不仅适用于汽车芯片设计和应用,对于数据中心、工业控制和高端消费电子等领域的芯片和方案而言,也在逐渐变得不可或缺。

为了让芯片能够更好地发挥性能,并具有出色的可靠性,各个行业都在持续优化芯片设计的标准,汽车行业是较为典型的,拥有AEC-Q100、ISO26262、AEC-Q004等一系列标准,以求车规级芯片能够在整个生命周期内稳定运行。

随着芯片和系统复杂度提升,想要让芯片满足相关标准已经变得愈发困难,满足标准的芯片被部署到现场之后,很多未测试的物理挑战正成为大麻烦,这在汽车驾驶应用中是不被允许的。

新思科技凭借全面的EDA工具、领先的IP方案,以及在云技术方面的前瞻布局,推出了行业领先的芯片生命周期管理(SLM)平台,为复杂芯片的设计和部署赋能。新思芯片生命周期管理(SLM)的出现,能够为开发人员提供各种设计帮助。当芯片部署之后,芯片生命周期管理(SLM)还能够持续提供可操作的优化建议,帮助开发人员应对设计和应用中的可靠性挑战,实现对产品全生命周期的数据及性能管理。(文章转自TechSugar,感谢关注)