Cadence:应对生成式AI变革 打造“芯片到系统”AI驱动EDA全平台

大模型支撑的生成式AI“热度”持续升温,不仅有望深度赋能千行百业,也在激发半导体产业链自上而下的深刻变革。

在今日开幕的2023 ICCAD上,Cadence 副总裁、中国区总经理汪晓煜在题为“步入芯片和系统设计新范式”的演讲中提到,摩尔定律不仅反映了半导体行业的发展规律,也推动了整个信息技术领域的创新和变革,人工智能、5G 通信、HPC、自动驾驶和工业物联网等新的应用需求、算力和能效要求对于芯片和系统设计提出了更高的要求。在此趋势下,芯片和系统设计的复杂性也不断增加,如何利用生成式AI解放生产力将成为制胜关键。Cadence厚积薄发,全面打造了“芯片到系统”的AI驱动EDA方案,助力全产业链共创共赢。

Cadence 副总裁、中国区总经理汪晓煜

第四次工业革命驱动EDA“AI”化

汪晓煜在开场中直言,半导体进步的核心推力是持续提升经济附加值,在半导体进入晶体管时代开始催生了一系列产品和应用繁荣,从大型计算机到家电,到个人电脑PC,再到智能手机,以及兴起的智能终端、智能汽车等等。

在摩尔定律的引领下,多重技术和多种应用共同驱动市场持续增长,半导体行业持续蓬勃发展。汪晓煜引用数据提到,预计到2030年,全球半导体规模将超过1万亿美元,而人工智能、5G 通信、HPC、自动驾驶和工业物联网等催生的智能电子系统市场也将提升至3万亿美元规模。

在经过第一次工业革命开启蒸汽机时代,第二次工业革命开启电气化时代,第三次工业革命开启自动化时代之后,汪晓煜认为,第四次工业革命开启的是后工业4.0时代,之前三次工业革命单一技术的变革来实现突破的,即从蒸汽机到电力再到计算机,在第四次工业革命早期互联网技术的普及推动了信息化。但在后工业4.0时代将从信息化转向数字化,AI成为驱动核心,半导体则承载着赋能AI的作用,通过AI和半导体技术的不断发展催生智能系统的应用和普及,进而才能推动整个社会的数字化转型。

而要构成一个真正意义上的智能系统,不只是芯片层面软硬件的结合,还必须实现一定的感知能力、学习能力和计算能力以及海量数据的融合。汪晓煜指出,整体而言,智能系统需要软硬件系统与AI的高度融合。

相应地,这也引发了EDA开发、芯片设计和智能系统融合的挑战。汪晓煜提到,摩尔定律推动工艺提升,线宽缩小势必带来更复杂和更大规模的设计。尽管考虑经济效益,可以采用先进封装设计,但对散热、信号完整性、良率和可靠性都带来一系列的挑战,基于传统EDA设计流程已然难以应对挑战。

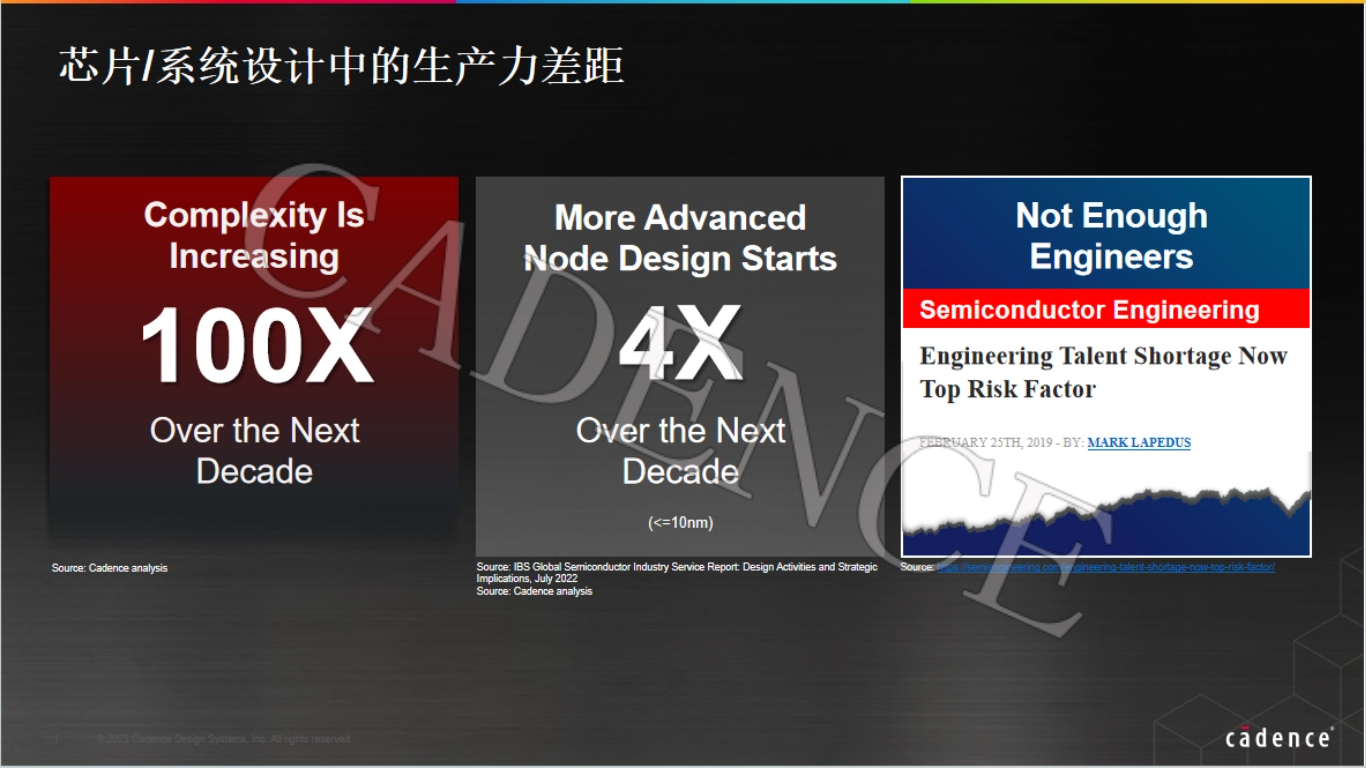

从芯片/系统设计中的生产力差距来看,汪晓煜指出,芯片复杂度将在下一个十年增长100倍,而采用先进节点设计的芯片规模才扩大4倍,鸿沟巨大,而且半导体人才短缺的挑战也十分严峻,应对这些挑战,AI驱动的EDA解决方案已成为“首选”。

对此汪晓煜进一步表示,传统的EDA工具都是单一工具和单一运行环境,如电路仿真、逻辑设计、验证工具等等,而在当下,先进制程和先进封装对数字EDA工具提出了更高要求。EDA工具需更快响应新需求,同时要更进一步的智能化,实现多运算、多引擎才能加快芯片迭代速度,支撑半导体业向后摩尔时代发展。AI可从设计数据中自主学习,从而为下一次执行自动做出优化的选择,进而最终减少设计人员的人工决策时间,大幅提升生产力,AI驱动的EDA解决方案则将带来生产力的下一次飞跃。有数据显示,无论是在晶体管设计、基于单元库的设计还是RTL设计复用层面,生产力均能提升10倍以上,在2030年将带来10倍的设计力提升。

汪晓煜进一步介绍,利用LLM技术将生成式AI扩展到设计流程中,可将个人和团队进行的Spec设计协同、项目集成等方面促进IP和芯片创新,同时提升验证和调试效率,促进生成式AI在数字设计方面的实施效率和PPA优化。有数据显示,生成式AI在设计流程中发挥了巨大作用,4nm服务器芯片设计中减少电源漏电提升28%,TPU设计减少PCB布线14%,汽车芯片设计中减少PCB信号损失135%,自动驾驶芯片提升调试效率6倍等等。

打造“芯片到系统”的AI驱动EDA方案

Cadence作为全球 EDA 行业的领导企业,面向下一代AI驱动的EDA工具需求,也在全面布局,并打造出了第一个全面的“芯片到系统”生成式AI工具平台,通过Cadence JedAI Platform的大数据分析,可以让AI执行的更加快速和有效率。每一个点工具的AI能力加持,对于芯片设计都极有帮助,而当所有的点工具都集合成一个统一的AI数据平台,进行数据的存储、分类、压缩和管理,则能实现生产力的极大提升以及功耗、性能和面积(PPA)的优化。

目前,通过JedAI Platform,Cadence统一管理了旗下各种AI平台的大数据分析——包括Verisium验证、Cerebrus物理实现、Optimality系统优化,Allegro X AI系统设计及Virtuoso Studio模拟设计等。

Cerebrus作为Cadence首款创新的基于机器学习的设计工具,可扩展数字芯片设计流程并使之自动化,让客户能够高效达成要求严苛的芯片设计目标。汪晓煜提到,Cerebrus在客户超过200款芯片流片过程中的战果辉煌,如在3nm多核CPU IP的漏电优化中提升38%、5nm GPU设计效率提升8倍、7nm智能驾驶SoC时序优化提升60%等。

随着SoC复杂性不断提高,验证往往比其他工程任务更加消耗算力和人力,如何缩短验证周期已成为产品按时上市的关键。汪晓煜指出,通过部署Verisium平台,汇集所有波形、覆盖率、报告和日志文件等验证数据于JedAI平台中,在此平台上建立机器学习模型和发掘更多特定指标,进而将其应用于全新系列工具上,从而极大地提高验证工作效率。从其表现来看,无论是10亿门手机SoC设计改进、存储控制器IP的快速抖动分析、RISC-V GPU的RTL改进验证,均可分别提升20、30和60倍,功力强大。

此外,一直以来PCB设计中的布局布线是一个耗时的手动过程,且影响上市速度。而Cadence推出的Allegro X AI技术,可自动执行器件摆放、金属镀覆和关键网络布线,并集成了快速信号完整性和电源完整性分析功能,为当前高速、高密度、多层的复杂PCB设计布线提高了生产力、优化了质量。汪晓煜介绍案例时说,使用Allegro平台的生成式AI功能,单层计算机开发板布局布线效率能提升57倍,消费IoT板布板时间能减少至48倍,自动驾驶PCB板的布局布线效率提升最高达39倍。

随着云计算、人工智能、自动驾驶、5G通信、工业物联网的发展,带动了高端芯片需求不断走高,芯片设计的复杂度和成本也在急速提升。据统计,5nm设计成本约为4亿美元,3nm则为5亿美元,2nm更是高达6.35亿美元,为支持Cadence智能系统设计战略,满足工艺迁移需求,减少流片成本和加快上市,Cadence 推出了全新的Virtuoso Studio工具。

据介绍,Virtuoso Studio支持在既定的工艺技术上重复使用现有的layout,通过自定义布局和自动化布线,在新的工艺技术上快速重建迁移后的layout。此外,还可以自动将源原理图的实例、参数、引脚和连线从一种工艺技术映射到另一种工艺技术。使用Virtuoso ADE仿真环境和基于AI的电路优化技术,可对映射的原理图进行优化和验证,确保更新后的原理图能够满足所有必要的设计规范。

可以看到,Cadence在EDA全流程领域的“AI”化带来了复杂芯片设计和PCB设计的大解放。

汪晓煜最后强调,Cadence将不断通过AI赋能和优化EDA方案,着力形成真正意义上的多模块、多功能设计,以全面提升开发效率,持续助力半导体全产业链在释放“生产力”的征程中加速前行,而这也将是芯片设计的未来。